芯片是现代电子设备的“大脑”,从手机、电脑到工业控制器、汽车ECU,无一不依赖芯片的正常运行。芯片引脚——芯片与外界通信的“神经末梢”——一旦出现故障,整个设备就可能陷入瘫痪。实际维修统计表明,相当比例的电路板故障根源就在于芯片引脚相关的虚焊、短路或内部损坏问题。对于电子维修人员、企业质检工程师和电子爱好者而言,掌握一套系统、可靠的测量芯片引脚好坏方法,不仅是排查电路故障的核心技能,更是提升维修效率和保障产品质量的必备能力。

本文以芯片引脚检测为主线,从封装类型识别到工具选用,从安全规范到实操方法,从常见误区到失效案例分析,分层次、分场景地系统讲解如何精准判断芯片引脚好坏。无论你是刚入行的维修新手,还是需要批量质检的专业工程师,都能从中找到适合自身场景的检测方案,快速掌握芯片引脚检测的核心技巧。

一、芯片引脚检测前置准备(适配消费电子/工业设备场景)

1. 芯片封装与引脚结构认知(识别引脚标识的“第一课”)

在动手检测之前,首先要弄清楚你面对的是哪种芯片封装。主流IC封装可分为四类:SOP/SOIC(小外形封装)、QFP(四方扁平封装)、QFN(方形扁平无引脚封装)和BGA(球栅阵列封装),它们的引脚结构、设计要点和检测风险完全不同-5。

SOP/SOIC:引脚外弯,两侧出脚,常见8脚、14脚、16脚,间距1.27mm,是最通用的小信号IC封装。SOP封装的引脚有明确的1号脚标识——通常用丝印圆点、缺口或斜角边标记,沿着标识逆时针数即可定位引脚顺序-5。

QFP:引脚四边外伸,间距常见0.5mm、0.4mm甚至0.3mm,引脚数32到144不等,多用于主控芯片和FPGA。高密度QFP封装的引脚检测尤其需要细心,因其引脚间距极小,手工测量时要特别注意避免相邻引脚短路-5。

QFN:无外露引脚,焊盘在封装底部四周,体积小、散热好,当前主流封装之一,如STM32常用QFN-32/48/64。QFN的引脚识别主要靠底部边缘焊盘的排列方向来确定1号脚位置-5。

BGA:引脚在底部呈阵列分布,间距0.8mm、0.65mm、0.5mm,引脚数可达数百,用于高端CPU、GPU和通信芯片。BGA封装的引脚检测是难度最高的——焊点隐藏在芯片底部,肉眼无法直接观测,必须借助X射线检测或专业测试夹具-5。

记住一个核心原则:检测前100%核对芯片数据手册(datasheet) 。无论是引脚的1号脚位置、各脚功能定义还是关键电气参数,都以数据手册为准。SOP重对称、QFP重间距、QFN重散热、BGA重扇出,吃透这四类封装的结构逻辑,就掌握了芯片引脚识别的基础-5。

2. 核心检测工具介绍(基础款+专业款)

基础款(新手/个人维修必备) :

数字万用表:芯片引脚检测的核心工具。建议选择内阻≥20MΩ的数字万用表,具备二极管档和蜂鸣通断档。万用表主要用于测量引脚间直流电阻、对地电阻和引脚电压。

放大镜/体视显微镜:用于观察引脚外观是否氧化、弯曲、开裂或焊接不良。消费电子维修场景中,60倍手持放大镜即可满足基本需求。

防静电腕带/工作台:芯片尤其是CMOS器件对静电极其敏感,操作前必须做好静电防护,佩戴防静电腕带并确保接地良好。

专业款(工厂批量/高精度检测场景) :

示波器:用于检测芯片引脚上的实时信号波形,验证时钟信号、数据信号和电源噪声是否符合规格。

逻辑分析仪:用于捕获多个引脚同时变化的数字信号时序,尤其适合I2C、SPI、UART等总线协议的波形分析-。

AOI(自动光学检测)设备:工业生产线上的主力检测工具,通过高分辨率工业相机对引脚进行多角度拍摄,可精准识别位置偏移、共面度异常、缺失等缺陷-。正位度检测系统精度可达0.001mm,检测速度达10次/秒-。

X射线检测设备:专门用于BGA封装的焊点检测,可透视芯片底部,检查虚焊、空洞和桥连等内部缺陷-33。

3. 芯片引脚检测安全注意事项(重中之重)

芯片引脚检测过程中,静电放电(ESD)是最大的隐形杀手。一个在人体几乎无法感知的静电释放,就足以导致芯片内部发生不可逆的损伤-63。以下安全要点必须严格遵守:

① 防静电是第一原则:操作前佩戴防静电腕带并连接到公共接地端,使用防静电工作台和防静电包装存放芯片。国家标准GB/T 37977.51-2023明确要求,对静电敏感度不低于HBM 100V的电子器件必须建立完善的ESD控制程序-。人体模型(HBM)ESD测试标准JS-001定义了芯片承受静电放电的标准化测试方法,日常操作中任何未做防护的接触都可能达到这个阈值-。

② 断电检测是必须遵守的底线:在测量芯片引脚对地电阻或通断性之前,务必切断电路板电源,并等待电容放电完毕。带电测量不仅可能损坏万用表,更可能因表笔滑动导致引脚间短路,瞬间烧毁芯片-68。

③ 避免引脚间意外短路:测量电压或波形时,表笔或探头不要因滑动而造成相邻引脚短路。建议在与引脚直接连通的外围印刷电路上测量,而不是直接在芯片引脚上操作,特别是对于QFP等高密度封装-68。可用一段气门芯套在表笔尖上,既能良好接触被测点,又能有效防止打滑-44。

④ 焊接操作注意事项:不允许带电使用烙铁焊接;使用内热式25W左右的电烙铁,焊接时间不超过3秒钟;烙铁外壳必须接地良好,对CMOS电路尤其要小心-68。

二、核心检测方法(从基础到专业,分层次实操)

1. 外观检查法(快速初筛,无需工具)

在动用任何仪器之前,先用肉眼或放大镜做一次全面外观检查。这个方法虽然基础,但往往能发现最明显的故障:

第一步:检查芯片是否安装反了方向。确认芯片的1号脚标识(丝印圆点、缺口、斜角边)与PCB板上的标识对应。

第二步:观察各引脚是否有氧化、发黑、弯曲、断裂或缺失现象。长时间存放的芯片引脚氧化后呈暗灰色,焊接时润湿性大幅下降,容易导致虚焊-33。

第三步:检查引脚焊点是否有虚焊、假焊或桥连。虚焊表现为焊点与引脚之间接触电阻过大,外观看似连接实则未形成有效导电通路,在设备使用过程中可能因振动或温度变化导致突然断路-。

第四步:观察芯片表面是否有烧糊、鼓包或裂纹。这些明显痕迹通常是芯片内部短路或过热的直接证据。

2. 万用表电阻法测量芯片引脚好坏(新手重点掌握)

万用表电阻法是芯片引脚检测最常用、最实用的方法,分为“离线检测”和“在线检测”两种场景:

(1)离线检测(芯片未焊接在电路板上)

这是芯片入库检验和新芯片验收的标准方法。方法如下:

第一步:将万用表置于电阻挡(建议用R×1k或R×10k挡),黑表笔接芯片的接地引脚(GND),红表笔依次测量其他各引脚对地的正向电阻-39。

第二步:记录每个引脚的电阻值。由于芯片内部含有大量非线性元件(三极管、二极管等),单测一个阻值不能判断好坏,必须互换表笔再测一次,获得正反向两个阻值。只有当正反向电阻值都符合数据手册或正常芯片的参考值时,才能判断该引脚正常-39。

第三步:与标准值对比。测量时万用表应选用同一挡位。如果因个别引脚电阻过大或过小需要更换挡位(如换R×10k挡),则测量正常芯片的同一引脚时也要换到同一挡位-。

(2)在线检测(芯片已在电路板上)

实际维修中,大多数情况是在路检测——芯片已经焊接在电路板上。此方法通过测量芯片各引脚在路直流电阻和电压来判断故障-44。

操作步骤:

第一步(电阻测量) :断电状态下,用万用表测量芯片各引脚对地的正反向电阻,与正常值对比。若某引脚电阻偏离正常值,可能是芯片内部损坏,也可能是外围元件故障导致,需要进一步排查-44。

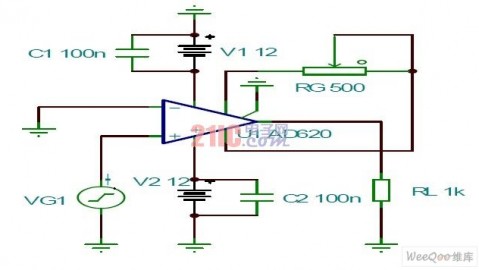

第二步(电压测量) :通电状态下,用万用表直流电压挡测量各引脚对地直流电压,与数据手册中的标准电压值对比-44。万用表内阻至少要大于被测电路电阻的10倍以上,否则会产生较大测量误差,建议使用内阻≥20KΩ/V的万用表-68。

第三步:若所有引脚电压正常,一般可认为芯片正常;若部分引脚电压异常,从偏离正常值最大处入手,先检查外围元件(电阻、电容、电感等)有无故障,若无外围故障,则芯片很可能损坏-44。

实用技巧:如果不想从电路板上焊下芯片,可以尝试将电压异常的引脚从电路中断开(切断相关走线或拆除外围元件),同时将接地脚也从电路板断开,保持其他引脚原状,然后测量该脚与接地脚之间的R内正反向电阻值,即可判断芯片是否损坏-39。

3. 示波器与逻辑分析仪检测法(进阶精准检测)

当万用表检测无法定位故障时,就需要用到更专业的工具。示波器和逻辑分析仪能“看见”芯片引脚上的实时信号,揭示那些电阻测量发现不了的“软故障”:

示波器检测:将示波器探头接地夹接PCB地线,探头触点在待测引脚上。重点检测三类引脚信号:①电源引脚——检查电压是否稳定,纹波是否在允许范围内;②时钟引脚——检查是否有稳定频率的方波信号,幅值是否符合规格;③数据/控制引脚——检查是否有信号变化,幅值是否正常。在实际故障排查中,示波器能让新手在短时间内判断出问题出在电源还是信号链路上,把“盲目试错”变成“精准定位”-。

逻辑分析仪检测:适用于需要同时观察多个引脚信号时序的场景。逻辑分析仪拥有从16到数百个测量通道,可以将同一时间多个引脚的I/O变化和相互间的关系显示在同一窗口上,方便工程师快速分析总线通信协议(如I2C、SPI、UART)的时序是否正常-。混合信号示波器(MSO)将示波器和逻辑分析仪的功能集成在一起,屏幕上可同时看到模拟信号和数字信号,是嵌入式系统调试的理想选择-53。

三、补充模块(行业实战干货)

1. 不同类型芯片引脚的检测重点

不同应用场景下的芯片,引脚检测的重点各不相同:

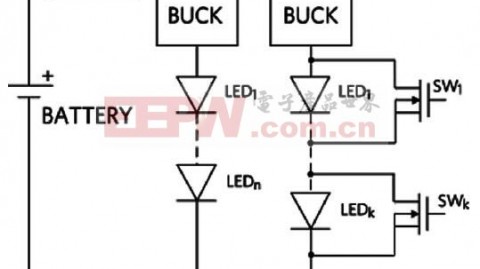

消费电子类芯片(手机、电脑、家电) :以SOP/QFP封装为主,重点检测电源引脚与地引脚之间的对地电阻(正常应≥数百欧姆),以及时钟引脚的信号完整性。常见故障为引脚氧化、弯曲和焊点虚焊-29。

汽车电子类芯片(ECU、传感器控制器) :以QFP、QFN和BGA封装为主,工作环境恶劣(高温、振动、湿度),检测重点在于引脚焊接可靠性和信号抗干扰能力。PIN针的高度一致性与位置精度是保障电气连接可靠性的核心前提,存在高度偏差或位置偏移时,轻则导致回流焊时虚焊,重则引发控制器功能失效甚至行车安全事故-。

工业控制类芯片(PLC、变频器、工控板) :以BGA和大尺寸QFP封装为主,长期运行在大电流、高电压环境下。检测重点包括:①电源引脚的过流保护能力;②信号引脚在强电磁干扰环境下的稳定性;③散热设计是否到位。BGA焊点空洞是影响长期可靠性的主要隐患,需要通过X射线检测才能发现-33。

通信设备类芯片(路由器、基站) :以BGA和高密度QFP封装为主,引脚数量多、间距小。检测重点在于高频信号的阻抗匹配和引脚共面度,共面度偏差可导致部分引脚接触不良,影响通信稳定性-12。

2. 芯片引脚检测常见误区(避坑指南)

根据行业统计数据,以下是芯片引脚检测中最容易踩坑的误区:

误区一:测量引脚电阻正常=芯片是好的 ❌

很多软故障(如内部PN结性能退化、阈值电压漂移)不会引起直流电阻的明显变化,但会导致芯片在某些工况下工作异常。电阻法只能排查硬损伤,不能排除软故障-44。

误区二:电压异常就直接换芯片 ❌

芯片引脚电压异常,很可能是外围元件(电阻、电容、电感)损坏导致的,盲目更换芯片不仅浪费,还可能因焊接操作损坏电路板。正确流程是:先排查外围元件,再判断芯片-68。

误区三:忽略静电防护直接用手接触芯片 ❌

人体携带的静电电压可达数千伏甚至上万伏,足以击穿芯片内部的极薄氧化层,造成不可逆的硬损伤或潜伏性缺陷-63。CMOS器件的输入引脚绝对不允许在未做静电防护的情况下触摸。

误区四:带电插拔芯片或测量引脚 ❌

带电操作极易因表笔滑动导致相邻引脚短路,瞬间大电流可能烧毁芯片。测量引脚电压前应先断电安装好表笔和探头,确认无误后再通电测量-44。

误区五:忽略环境因素对检测结果的影响 ❌

温度、湿度、电源电压波动都会影响芯片引脚的电气参数。高精度检测应在标准环境条件下进行,测量数据应与数据手册中规定的条件匹配。

3. 芯片引脚失效典型案例

案例一:芯片引脚塌丝导致输出对地短路(封装工艺缺陷)

某反馈电路在使用中出现异常,5块样品中有4块无法通过出厂检测,主要失效表现为静态电流异常、输出电压异常。经X射线检查发现,失效芯片的输出引脚内部铜丝过长,在靠近第二焊点处塌丝,碰到芯片底座后与GND短路-69。进一步分析发现,该问题源于封装过程中的键合工艺控制不当,塌丝导致输出脚与地之间形成永久性短路通道-69。

启示:塌丝属于封装工艺缺陷,常规的万用表检测只能发现短路故障,但无法定位塌丝的具体位置,需要借助X射线等专业检测手段才能锁定根源。

案例二:BGA芯片焊点开裂导致设备间歇性故障

某工业控制器在使用一段时间后出现间歇性故障,设备时好时坏,振动环境下故障频发。经分析,BGA封装芯片的多个引脚焊点呈贯穿性开裂,开裂位于PCB侧IMC与焊锡之间-。失效原因在于芯片与PCB的热膨胀系数(CTE)不匹配,回流焊后长期热循环导致焊点疲劳开裂-33。

启示:间歇性故障的根源往往是BGA焊点开裂,这种故障在常温下电阻测量可能正常,但在高温或振动环境下失效才会显现。检测时需要结合热循环试验和环境应力筛选。

四、结尾

1. 芯片引脚检测核心(高效排查策略)

掌握一套分级检测策略,能让芯片引脚检测事半功倍:

| 检测层级 | 适用场景 | 核心方法 | 预期目标 |

|---|---|---|---|

| 一级:外观检查 | 所有场景(入门级) | 目视+放大镜观察 | 排除明显故障(方向反、氧化、弯曲、虚焊) |

| 二级:万用表电阻法 | 个人维修、样品初筛 | 离线/在线电阻测量 | 判断芯片内部直流等效电阻是否正常 |

| 三级:万用表电压法 | 电路板故障定位 | 通电测各脚电压 | 压缩故障范围,定位异常引脚 |

| 四级:示波器/逻辑分析仪 | 信号完整性排查 | 测波形、时序分析 | 排除/定位软故障和时序问题 |

| 五级:专业检测设备 | 批量质检、失效分析 | AOI、X射线、ICT | 高精度、高效率批量检测 |

核心逻辑:从简单到复杂,从外部到内部,先不伤芯片(电阻法)后上电检测(电压法),先易后难逐步推进。遇到检测结果异常时,优先排查外围元件,再判断芯片是否损坏。

2. 芯片引脚检测价值延伸(日常维护与采购建议)

日常维护技巧:①定期检查PCB板上芯片引脚是否有氧化迹象,存放环境保持干燥(湿度<60%);②操作前务必做好静电防护,使用防静电腕带和工作台;③维修时使用低温电烙铁,焊接时间控制在3秒以内,避免热损伤。

采购建议:①从正规渠道采购芯片,避免使用翻新或散新芯片,因其引脚可能存在不可见的质量隐患;②收货后尽快做万用表电阻法入库检测,记录各引脚的正反向电阻值作为基准;③对BGA等精密封装芯片,建议采用X射线抽检,确认无空洞、桥连等工艺缺陷。

校准建议:万用表和示波器应定期校准,确保测量精度。工厂产线的AOI设备需按IPC/JEDEC标准(如J-STD-002E)进行周期验证,保证检测准确性-。

3. 互动交流(分享你的芯片引脚检测难题)

你在芯片引脚检测过程中,是否遇到过以下情况?欢迎在评论区分享你的经历:

万用表测出来引脚电阻正常,但上电后芯片就是不工作,最后发现是哪里出了问题?

BGA封装的芯片虚焊,你是如何快速定位到故障引脚的?

在汽车电子或工业设备维修中,有没有遇到过因环境因素(高温、振动、潮湿)导致的引脚失效?

如果你觉得这篇文章对你有帮助,欢迎收藏和转发给更多需要的同行。关注本账号,获取更多电子元器件检测实操干货。下期预告:《BGA封装焊点检测全攻略——X射线+电气检测双管齐下》!